이번 주는 다른 분들 정리를 보니

내가 공부를 제대로 안 하고 있음을 또 깨달았다 😂

공부랑 안 맞는 걸 알지만

복학을 위해 해야하는걸 어째 ..

그래도 뭔가 꾸준히 하는게 생겨서 뿌듯ㅎ ㅏ ㄷ ㅏㅏ ‼️‼️

정리하기 복잡했던 부분들은 추후 정리해서 추가로 올리도록 하겠습니다.. 🫥🔥

진짜 다음 주는 제대로 정리한 것까지 제때 올리기 ...

chapter 04 CPU의 작동 원리

04 - 1 ALU와 제어장치

ALU : 계산하는 장치

1) 받아들이는 정보

계산을 하기 위해서는 피연산자와 수행할 연산이 필요함.

레지스터를 통해 피연산자 받아들임

제어장치로부터 수행할 연산을 알려주는 제어신호 받아들임.

2) 내보내는 정보

연산을 수행한 결괏값 ( 숫자, 문자, 메모리 주소 .. ) → 일시적으로 레지스터에 저장 (CPU가 메모리에 접근하는 속도가 레지스터에 접근하는 속도보다 훨씬 느림 !!)

연산 결과에 대한 추가적인 상태 정보(이진수의 양수, 음수 ..)인 플래그를 내보냄

+) 부호 •제로 • 캐리 • 오버플로우 • 인터럽트 • 슈퍼바이저 플래그 등의 여러 종류가 있다.

+) 연산 결과가 결과를 담을 레지스터보다 큰 상황을 오버플로우라고 한다.

제어장치: 제어 신호를 내보내고, 명령어를 해석하는 부품

제어 신호 : 컴퓨터 부품들을 관리하고 작동시키기 위한 일종의 전기 신호

1) 받아들이는 정보

- 클럭 신호를 받아들인다

클럭 : 컴퓨터의 모든 부품을 일사불란하게 움직일 수 있게 하는 시간 단위

- '해석해야 할 명령어'를 받아들인다.

명령어 레지스터 → '해석해야 할 명령어' → 제어장치 → 제어신호 → 컴퓨터 부품들에게 수행할 내용 알리기

- 플래그 레지스터 속 플래그 값을 받아들인다.

플래그는 제어장치가 제어 신호를 통해 컴퓨터 부품들을 제어할 때 중요한 참고 사항 역할

- 시스템 버스, 그중에서 제어 버스로 전달된 제어 신호를 받아들인다.

제어 버스를 통해 외부로부터 전달된 신호를 받아들이기도 한다.

2) 내보내는 정보

- CPU 내부에 전달

레지스터 : 레지스터 간의 정보이동이나 값의 저장 등의 레지스터를 움직이게 하는 신호

ALU : 수행할 연산에 관한 제어 신호

- CPU 외부에 전달

메모리 : 메모리 읽어라, 써라... 등의 지시 신호

입출력장치: 입출력장치 읽어라, 써라... 등의 동작 지시

04 - 2 레지스터

레지스터 : CPU 내부의 작은 임시저장장치

→ 프로그램 속 명령어 & 데이터는 실행 전후로 레지스터에 저장

→ CPU 내부에는 다양한 레지스터들이 있고, 각기 다른 역할을 한다.

<반드시 알아야 할 레지스터 >

- 프로그램 카운터

- 명령어 레지스터

- 메모리 주소 레지스터

- 플래그 레지스터

- 범용 레지스터

- 스택 포인터

- 베이스 레지스터

1) 프로그램 카운터

메모리에서 가져올 명령어이 주소 ( 메모리에서 읽어 들일 명령어의 주소 )

instruction pointer (명령어 포인터)라고 부르는 CPU도 있다.

2) 명령어 레지스터

해석할 명령어 ( 방금 메모리에서 읽어 들인 명령어 )

제어장치가 해석한다.

3) 메모리 주소 레지스터

메모리의 주소

CPU가 읽어들이고자 하는 주소를 주소 버스로 보낼 때 거치는 레지스터

4) 메모리 버퍼 레지스터

메모리와 주고받을 값 (데이터와 명령어)

CPU가 정보를 데이터 버스로 주고받을 때 거치는 레지스터

5) 플래그 레지스터

연산 결과 또는 CPU 상태에 대한 부가적인 정보 ( 저장하고 있는 레지스터)

6) 범용 레지스터

다양하고 일반적인 상황에서 자유롭게 사용할 수 있는 걸 말함

7) 스택 포인터

스택의 꼭대기를 가리키는 레지스터 ( 스택이 어디까지 차 있는지에 대한 표시 )

즉, 스택에 마지막으로 저장한 값의 위치를 저장하는 레지스터.

8) 베이스 레지스터

GPT 설명으로는 .. 메모리 주소 계산 시 시작 위치를 나타내는 레지스터로 사용됨.

베이스 레지스터 주소 지정 방식에서 '기준 주소'로 역할을 함

특정 레지스터를 이용한 주소 지정 방식

04 - 3 명령어 사이클과 인터럽트

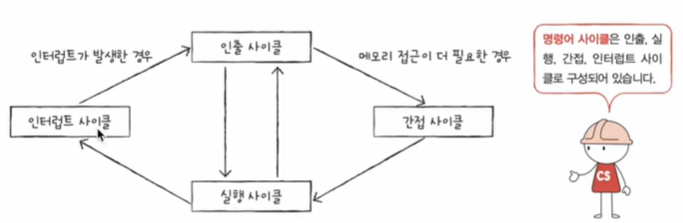

CPU가 명령어를 정해진 흐름대로 처리하는 것을 명령어 사이클이라고 함.

간혹 이 흐름이 끊기는 상황을 인터럽트라고 한다.

명령어 사이클

프로그램 속 명령어들은 일정한 주기가 반복되며 실행된다.

이 주기를 명령어 사이클이라고 함

인출 사이클 : 메모리에 있는 명령어를 cpu로 가지고 오는 단계

실행 사이클 : cpu로 가져온 명령어를 실행하는 단계

일부 : 인출 - 실행 - 인출 - 실행 - ….

✅BUT CPU로 명령어를 가지고 와도 바로 실행이 불가능한 경우

간접 사이클 : 메모리 접근이 더 필요한 경우에는 간접 사이클을 통해 메모리 접근을 한 번 더 함

인터럽트

CPU의 정상적인 작업을 방해하는 신호

INTERRUPT : 방해하다, 중단하다

- ‘CPU가 꼭 주목해야 할 때’, ‘CPU가 얼른 처리해야 할 다른 작업이 생겼을 때’ 발생

- 동기 인터럽트 (예외) / 비동기 인터럽트 ( 하드웨어 인터럽트 )

- 동기 인터럽트 (예외 exception)

CPU가 예기치 못한 상황을 접했을 때 발생

2. 비동기 인터럽트 (하드웨어 인터럽트 )

주로 입출력장치에 의해 발생

알림(세탁기 완료 알림 같은)과 같은 역할

CPU가 프린터와 같은 입출력장치에 입출력 작업을 부탁하면 작업을 끝낸 입출력장치가 CPU에 완료 알림(인터럽트)를 보낸다.

하드웨어 인터럽트

- 알림과 같은 인터럽트

- 입출력 작업 도중에도 효율적으로 명령어를 처리하기 위해 하드웨어 인터럽트 사용

- 입출력 장치는 CPU에 비해 느림

- 인터럽트가 없다면 CPU는 프린트 완료 여부를 확인하기 위해 주기적으로 확인해야 함.

- 인터럽트가 있다면 입출력 작업 동안 CPU는 다른 일을 할 수 있다.

인터럽트 요청 신호

: 정상적인 실행 흐름을 끊는 것이라 다른 누군가가 인터럽트 하기 전에 cpu에 물어보기

인터럽트 플래그

: 요청 받아들이려면 플래그 레지스터 속 인터럽트 플래그를 확인한다. (모든 인터럽트를 인터럽트 플래그로 막을 수 있는 것은 아니다) 대부분은 가능 !

인터럽트 서비스 루틴 실행 (메모리 안에 실행되는 프로그램임 / 인터럽트 핸들러 )

- 인터럽트가 발생했을 때 해당 인터럽트를 어떻게 처리하기 위한 프로그램

- 프로그램이기에 메모리에 저장

인터럽트 벡터: 각각의 인터럽트를 구분하기 위한 정보

‘ cpu가 인터럽트를 처리한다 ‘

== ‘인터럽트 서비스 루틴을 실행하고, 본래 수행하던 작업으로 다시 되돌아온다’

(+ 그리고 인터럽트의 시작 주소는 인터럽트 벡터를 통해 알 수 있다. )

Chapter 05 CPU 성능 향상 기법

05 - 1 빠른 CPU를 위한 설계 기법

클럭 속도는 CPU 속도 단위로 간주되기도 한다.

클럭 속도 : 헤르츠 (Hz) 단위로 측정

+) 클럭 속도는 일정하지 않다. → 최대 클럭 속도를 강제로 끌어올리는 기법을 오버클럭킹(overclocking)이라고 함.

필요 이상으로 클럭을 높이면 발열이 심해진다.

클럭 이외에 CPU를 빠르게 설계하는 방법

→ 코어 수 / 스레드 수 를 늘리는 방법

코어와 멀티 코어

코어 (core)

→ 우리가 지금까지 부른 CPU의 정의('명령어를 실행하는 부품')는 오늘날 코어라는 용어로 사용됨.

→ CPU는 '명령어를 실행하는 부품을 여러 개 포함하는 부품으로 확장됨. (오늘날)

→ CPU 내에서 명령어를 실행하는 부품으로 여러 개 있을 수 있다.

멀티 코어

멀티코어 프로세서

여러 개의 코어를 포함하고 있는 CPU를 말한다.

- 코어 수에 비례하여 CPU의 연산 속도가 증가하지는 않는다 !

- 중요한 것은 코어마다 처리할 명령어들을 얼마나 적절하게 분배하느냐이고 그에 따라서 연산 속도는 크게 달라진다.

스레드와 멀티 스레드

스레드

- 사전 의미 : ‘실행 흐름의 단위 ‘

- 하드웨어적 스레드 / 소프트웨어적 스레드

1) 하드웨어 스레드 : 하나의 코어가 동시에 처리하는 명령어 단위

== 멀티 스레드 프로세서

== 멀티 스레드 CPU

소프트웨어 스레드

하나의 프로그램에서 독립적으로 실행되는 단위

1 코어 1 스레드 cpu도 여러 소프트웨어적 스레드로 만들어진 프로그램을 실행할 수 있다.

멀티스레드 프로세서

하나의 코어로 여러 명령어를 동시에 처리하는 기술인 하드웨어적 스레드.

레지스터 세트가 한 개인 CPU는 한 개의 명령어를 처리하기 위한 정보들을 기억할 뿐

세트가 두 개인 CPU는 두 개의 명령어를 처리하기 위한 정보들을 기억할 수 있음.

위와 같은 경우에서는 하나의 코어에서 두 개의 명령어가 동시에 실행된다.

위와 같은 경우로 인해 하드웨어 스레드를 논리 프로세서라고 부르기도 함.

05 - 2 명령어 병렬 처리 기법

CPU가 시간을 알뜰하게 쓰면서 명령어를 처리하는 방법이 있을지 ?!

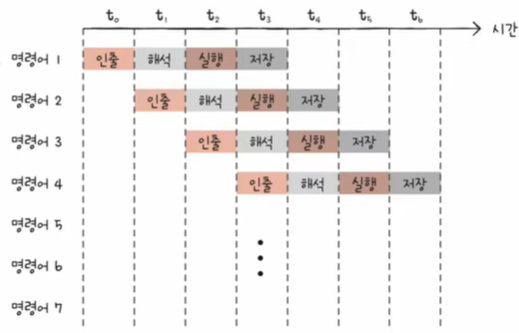

명령어 파이프라인

하나의 명령어가 처리되는 과정을 비슷한 시간 간격으로 나눠 보아야 한다.

명령어 인출 → 명령어 해석 → 명령어 실행 → 결과 저장

같은 단계가 겹치지만 않는다면 CPU는 ‘각 단계를 동시에 실행할 수 있다’

명령어 파이프라이닝 : 동시에 여러 개의 명령어를 겹쳐 실행하는 기법

파이프라인 위험 : 명령어 파이프라인이 성능 향상에 실패하는 경우

데이터 위험 : 명령어 간의 의존성에 의해 야기

- 모든 명령어를 동시에 처리할 수는 없다

- 이전 명령어를 끝까지 실행해야만 비로소 실행할 수 있는 경우

제어 위험 : 프로그램 카운터의 갑작스러운 변화

이를 위해 사용하는 분기 예측이라는 기술. 프로그램이 어디로 분기할지 미리 예측한 후 그 주소를 인출하는 기술

구조적 위험 : 서로 다른 명령어가 같은 CPU 부품 (ALU, 레지스터)를 쓰려고 할 때 발생한다.

슈퍼스칼라

CPU 내부에 여러 개의 명령어 파이프라인을 포함한 구조

이론적으로는 파이프라인 개수에 비례하여 처리 속도 증가

✅BUT 파이프라인 위험도의 증가로 인해

파이프라인 개수에 비례하여 처리 속도가 증가하진 않는다.

비순차적 명령어 처리 (OoOE : Out-of-order execution)

- 현대 CPU 발전에 기여한 중요 개념 !

- 명령어들 간의 합법적인 새치기

- 파이프라인의 중단을 방지하기 위해 명령어를 순차적으로 처리하지 않는 명령어 병렬 처리 기법이다.

- 아무 명령어가 순서를 바꿀 수는 없다. (의존성이 없는 명령어만 바꿀 수 있음 .. )

05 - 3 CISC 와 RISC

명령어가 파이프라이닝하기에 유리하게 생기려면 어떻게 생겨야할까???

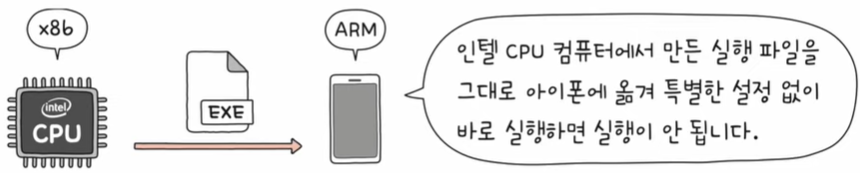

명령어 집합 (명령어 집합 구조, ISA : Instruction Set Architecture)

CPU가 이해할 수 있는 명령어들의 모음 ( CPU마다 ISA가 다를 수 있음 )

ISA(명령어 집합)의 두 축 : CISC & RISC

CISC (Complex Instruction Set Computer)

복잡한 명령어 집합을 활용하는 컴퓨터(CPU)

x86, x86-64는 CISC기반 명령어 집합 구조 (인텔)

복잡하고 다양한 명령어 활용

CISC 활용 명령어는 수행 시간이 길고 가지각색

RISC (Reduced Instruction Set Computer )

명령어의 종류가 적고, 짧고 규격화된 명령어 사용

단순하고 적은 수의 고정 길이 명령어 집합을 활용한다.

메모리 접근 최소화(load, store) 추구, 레지스터 십분 활용 ( load-store 구조라고 부르기도 한다)

다만 명령어 종류가 cisc보다 적기에 더 많은 명령어로 프로그램을 동작시킴

✅정리

기본 미션 )

P.125 확인 문제 2번

(1) 플래그 레지스터

(2) 프로그램 카운터

(3) 범용 레지스터

(4) 명령어 레지스터

P.155 확인 문제 4번

멀티코어는 CPU가 코어를 여러 개 가졌을 때를 말함.

빈칸 : 코어

'혼공컴운' 카테고리의 다른 글

| [혼공컴운] Ch 12~13 __ 혼공학습단 11기 5주차 (1) | 2024.02.08 |

|---|---|

| [혼콩컴운] Ch 09 ~ 11 __ 혼공학습단 11기 4주차 (2) | 2024.01.31 |

| [혼공컴운] Ch 06 ~ 08 _ 혼공학습단 11기 3주차 (2) | 2024.01.21 |

| Chapter 04-2 레지스터 (2) | 2024.01.14 |

| [혼공컴운] Chapter 01 ~ 03 _ 혼공학습1주차 (0) | 2024.01.07 |